# POLYMORPHIC PIPELINE ARRAY: A FLEXIBLE MULTICORE ACCELERATOR FOR MOBILE MULTIMEDIA APPLICATIONS

by

#### Hyunchul Park

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2009

#### Doctoral Committee:

Associate Professor Scott A. Mahlke, Chair Professor Trevor N. Mudge Professor James S. Freudenberg Assistant Professor Satish Narayanasamy Dr. Hong-seok Kim, Bain & Company © Hyunchul Park 2009 All Rights Reserved

#### ACKNOWLEDGEMENTS

This dissertation would not have been possible without the guidance and support of many people. First and foremost, I would like to thank my advisor, Scott Mahlke. His insight, expertise, enthusiasm, and encouragement played a large part in my success in graduate school. Without his guidance, this dissertation would not exist.

I would also like to thank my thesis committee, Professors Trevor Mudge, James Freudenberg, Satish Narayanasamy, and Dr. Hong-Seok Kim. They donated their time, providing valuable comments and suggestions that helped me refine my thesis.

The research presented in this dissertation is not the work of one person; I was fortunate to have the assistance of a number of other students in the Compilers Creating Custom Processors research group. In particular, Kevin Fan gave me valuable help in virtually every aspect of my graduate school life: debugging codes, writing papers, and even fixing my long-suffering 240sx. Manjunath Kudlur also contributed significantly, helping me write my first publication. More recently, Yongjun Park has been unfailingly supportive in performing hardware experiments for the token network and the PPA.

I would also like to thank people at Samsung Advanced Institute of Technology:

Sukjin Kim, Heeseok Kim and Taewook Oh. They helped me set up the compiler environment for my research and provided numerous application benchmarks that were extensively used in my dissertation.

As much as those who provided technical expertise, those who offered engaging conversation and moral support were crucial to my graduate school experience, namely: Amin Ansari, Jay Blome, Hyounkyu Cho, Mike Chu, Nate Clark, Ganesh Dasika, Shuguang Feng, Shantanu Gupta, Jeff Hao, Amir Hormati, Po-Chun Hsu, Steve Lieberman, Yuan Lin, Mojtaba Mehrara, Rob Mullenix, Rajiv Ravindran, Mark Woh, and Hongtao Zhong. I have shared offices, and in many cases, homes with these friends, and my time in Ann Arbor would not have been the same without them.

I would like to thank my family for their support, encouragement, and advice. My parents and my brother Sungchul provided their unconditional love and support throughout this whole process. Finally, I am grateful to You-sun Chung for her love and support. The occasional carrot and/or stick she would offer presumably to ward off procrastination and keep me on track seemed to yield uneven results at best. That is, until now.

# TABLE OF CONTENTS

| ACKNOWLE    | DGEMENTS                                     | ii  |

|-------------|----------------------------------------------|-----|

| LIST OF FIG | URES                                         | vii |

| LIST OF TAE | BLES                                         | Х   |

| ABSTRACT    |                                              | xi  |

| CHAPTERS    |                                              |     |

| 1 Introd    | uction                                       | 1   |

| 1.1         | Optimizations for CGRAs                      | 5   |

|             | 1.1.1 Compiler Support                       | 5   |

|             | 1.1.2 Control Path Optimization              | 6   |

| 1.2         | Polymorphic Pipeline Array                   | 7   |

| 2 Backgr    | round and Motivation                         | 8   |

| 2.1         | CGRA Overview                                | 8   |

| 2.2         | Modulo Scheduling Challenges                 | 10  |

| 3 Modul     | o Graph Embedding                            | 14  |

| 3.1         | Introduction                                 | 14  |

| 3.2         | Modulo Graph Embedding                       | 15  |

|             | 3.2.1 General Concepts                       | 16  |

|             | 3.2.2 Implementation                         | 28  |

| 3.3         | Experimental Results                         | 34  |

|             | 3.3.1 Experimental Setup                     | 34  |

|             | 3.3.2 Evaluation of Affinity Graph Heuristic | 35  |

|             | 3.3.3 Evaluation of Modulo Scheduler         | 36  |

| 3.4         | Related Work                                 | 39  |

|             | 3.4.1 Architectures                          | 39  |

|             | 3.4.2 Compilation Techniques                 | 40  |

| 3.5         | Summary                                      | 42  |

| 4 | Edge-o | centric Modulo Scheduling                              |

|---|--------|--------------------------------------------------------|

|   | 4.1    | Introduction                                           |

|   | 4.2    | Core Concepts                                          |

|   |        | 4.2.1 Integrated Placement and Routing                 |

|   |        | 4.2.2 Routing Cost Metrics                             |

|   |        | 4.2.3 Stage Re-assignment                              |

|   |        | 4.2.4 Edge Categorization                              |

|   | 4.3    | Implementation                                         |

|   |        | 4.3.1 Prepass Steps                                    |

|   |        | 4.3.2 Edge-centric Modulo Scheduler                    |

|   |        | 4.3.3 Postpass Steps                                   |

|   | 4.4    | Experimental Results                                   |

|   | 1.1    | 4.4.1 Experimental Setup                               |

|   |        | 4.4.2 Results                                          |

|   |        | 4.4.3 Analysis and Discussion                          |

|   | 4.5    | Related Work                                           |

|   | 4.6    |                                                        |

|   | 4.0    | Summary                                                |

| 5 | Contro | ol Path Optimization                                   |

|   | 5.1    | Introduction                                           |

|   | 5.2    | Motivation                                             |

|   | 5.3    | Dynamic Discovery of Instruction Formats               |

|   |        | 5.3.1 Concepts                                         |

|   |        | 5.3.2 Token Network                                    |

|   |        | 5.3.3 Supporting Modulo Scheduled Loops 89             |

|   | 5.4    | Configuration Memory Partitioning                      |

|   | 5.5    | Experiments                                            |

|   |        | 5.5.1 Experimental Setup                               |

|   |        | 5.5.2 Configuration Memory Partitioning                |

|   |        | 5.5.3 Token Network Evaluation                         |

|   | 5.6    | Summary                                                |

|   |        |                                                        |

| 6 | Polym  | orphic Pipeline Array                                  |

|   | 6.1    | Introduction                                           |

|   | 6.2    | Analysis of Multimedia Applications                    |

|   |        | 6.2.1 Fine Grain Parallelism                           |

|   |        | 6.2.2 Coarse-Grain Pipeline Parallelism                |

|   |        | 6.2.3 Computation Variance                             |

|   |        | 6.2.4 Summary and Insights                             |

|   | 6.3    | Polymorphic Pipeline Array                             |

|   |        | 6.3.1 Overview                                         |

|   |        | 6.3.2 Core Description                                 |

|   |        | 6.3.3 Supporting Coarse-Grain Pipeline Parallelism 120 |

|   |        | 6.3.4 Supporting Fine-Grain Pipeline Parallelism 120   |

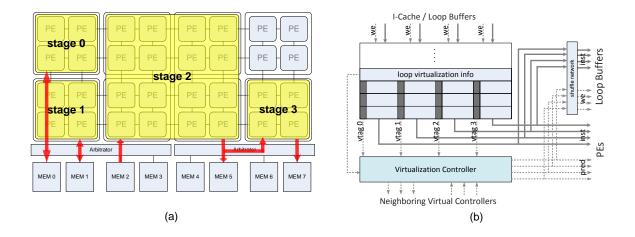

|           | 6.3.5 Hardware Support for Virtualization      | 122 |

|-----------|------------------------------------------------|-----|

| 6.4       | Compiler Support for Virtualization            | 123 |

|           | 6.4.1 Edge-centric Modulo Scheduling           | 123 |

|           | 6.4.2 How to Virtualize                        | 124 |

|           | 6.4.3 Virtualized Modulo Scheduling            | 127 |

| 6.5       |                                                |     |

|           | 6.5.1 Virtualized Modulo Scheduling Evaluation | 134 |

|           | 6.5.2 Performance Evaluation of PPA            | 135 |

|           | 6.5.3 Power and Area Measurement               | 139 |

| 6.6       | Related Works                                  | 140 |

| 6.7       | Summary                                        | 142 |

| 7 Concl   | usion                                          | 144 |

| 7.1       | Summary                                        | 144 |

| 7.2       |                                                |     |

| BIBLIOGRA | PHY                                            | 148 |

## LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1    | Example CGRA design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9        |

| 2.2    | Example to illustrate the challenges of CGRA scheduling: (a) the dataflow graph for the fsed application, (b) the reservation table for a partial schedule on a 4x4 array, (c) possible routings from 23's producers. In (a) and (b), dark grey shading indicates memory operations and light grey shading is used to highlight the current operation being scheduled (node 23) and its immediate predecessors. Bold numbers indicate computation operations, other numbers followed by 'r' (e.g. '8r') indicate routing slots for corresponding computation operations. | 1.0      |

| 3.1    | 'reg' nodes indicate live-in values stored in the central RF Modeling resources in a CGRA: (a) example 2x2 CGRA, (b) resource management model for 2x2 CGRA with II=3                                                                                                                                                                                                                                                                                                                                                                                                    | 10<br>17 |

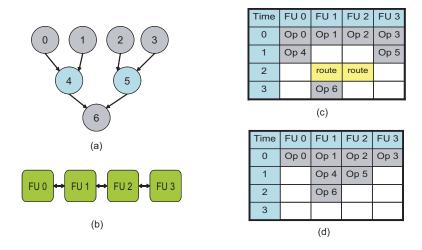

| 3.2    | Example showing the placement of producers affects the routing cost of consumers: (a) DFG for loop, (b) target architecture which is a 1x4 CGRA, (c) poor schedule that results in an extra cycle for routing values to Op 6, and (d) good schedule that results in no additional routing                                                                                                                                                                                                                                                                                | 19       |

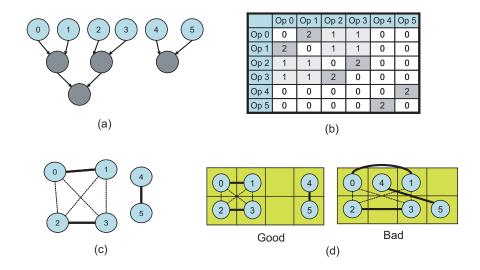

| 3.3    | Example affinity graph: (a) DFG for loop, (b) calculated affinities between each pair of operations, (c) affinity graph, and (d) possible operation assignments to a 2x4 CGRA                                                                                                                                                                                                                                                                                                                                                                                            | 22       |

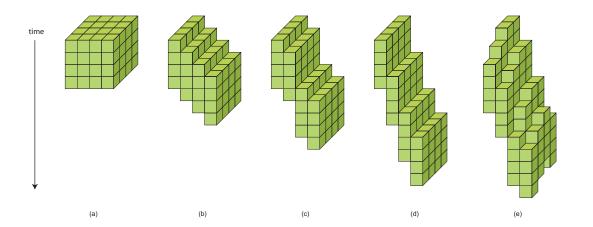

| 3.4    | CGRA scheduling spaces: (a) normal scheduling space, (b) skewed scheduling space, (c,d,e) variations of skewed scheduling space                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23       |

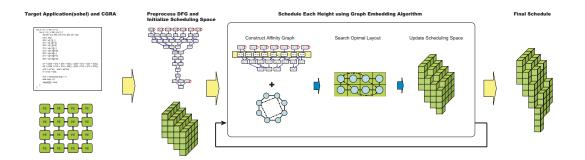

| 3.5    | Overview of the CGRA scheduling system: input is the assembly code<br>for the loop body and a description of the CGRA; preprocessing an-<br>alyzes the loop to compute heights and skew the available scheduling<br>cycles for the FUs; the graph is iteratively scheduled at successive<br>dependence height levels by constructing the affinity graph and per-                                                                                                                                                                                                         | _3       |

|        | forming modulo graph embedding of the affinity graph on the CGRA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28       |

| 3.6    | Scheduling process for operations at each successive dependence height.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32       |

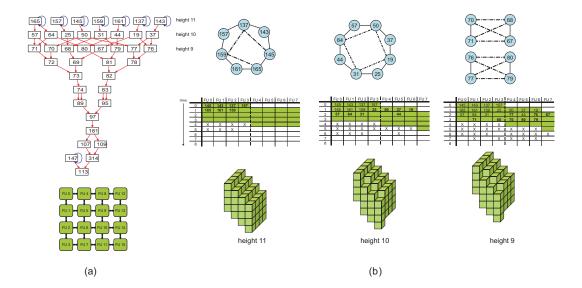

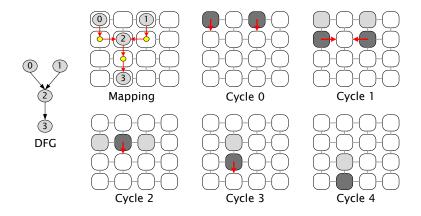

| 3.7  | Example of modulo graph embedding: (a) DFG of sobel and target CGRA, (b) scheduling results of first three heights                                                                                                                                                                                                     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

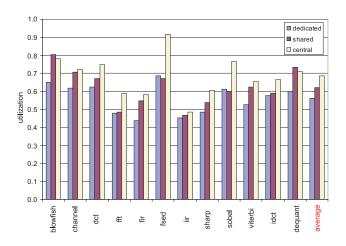

| 3.8  | Comparison of utilization rates for three register file configurations                                                                                                                                                                                                                                                 |

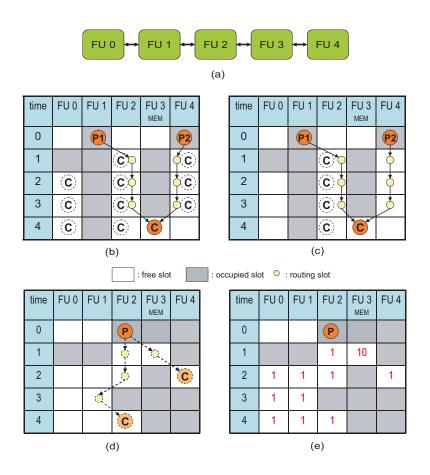

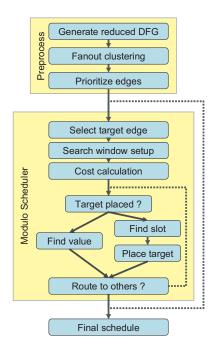

| 4.1  | High level comparison of scheduling approaches: (a) 1x5 CGRA, (b) compile time example of node-centric, (c) compile time example of edge-centric, (d) performance example of node-centric, (e) performance example of edge-centric. Shaded boxes in the reservation tables indicate slots occupied by other operations |

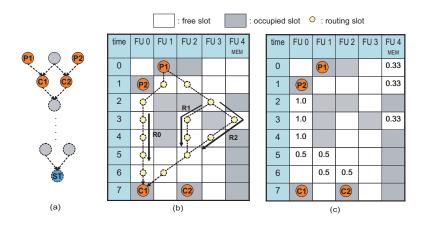

| 4.2  | Routing cost example: (a) dataflow graph, (b) possible mappings, and (c) probabilistic cost                                                                                                                                                                                                                            |

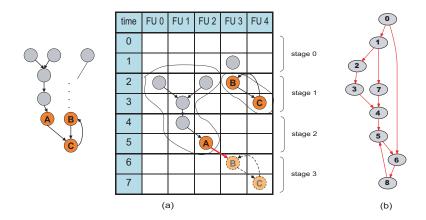

| 4.3  | (a) Stage re-assignment example (II = 2) that re-assigns the recurrence cycle B-C from time 2-3 to time 6-7 after operation A is scheduled; (b) Example dataflow graph to illustrate non-critical edges                                                                                                                |

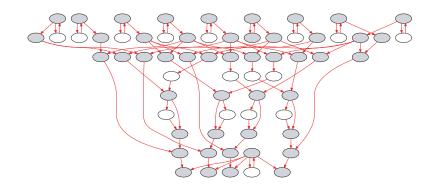

| 4.4  | An example dataflow graph from H.264                                                                                                                                                                                                                                                                                   |

| 4.5  | Example from Figure 4.4 after fanout clustering                                                                                                                                                                                                                                                                        |

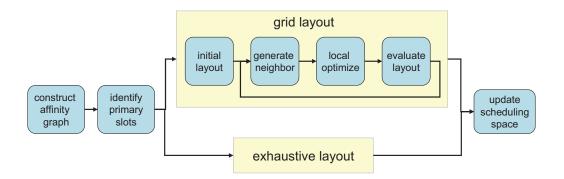

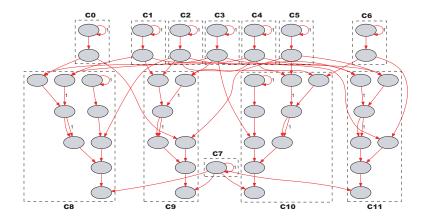

| 4.6  | System flow for edge-centric modulo scheduling                                                                                                                                                                                                                                                                         |

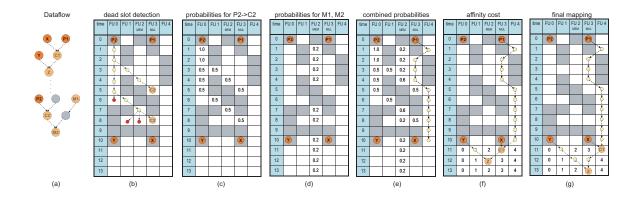

| 4.7  | Routing cost calculation example: (a) dataflow graph, (b) - (g) reservation table with computed routing costs                                                                                                                                                                                                          |

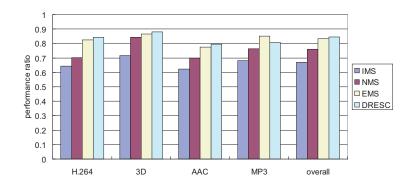

| 4.8  | Performance comparison of scheduling strategies for the mesh-plus architecture. The fraction of the theoretical maximum performance is plotted                                                                                                                                                                         |

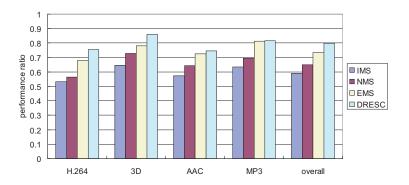

| 4.9  | Performance comparison of scheduling strategies for the mesh-only architecture                                                                                                                                                                                                                                         |

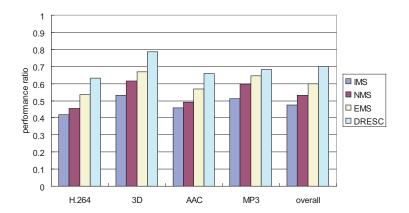

| 4.10 | Performance comparison of scheduling strategies for the no-RF-sharing architecture                                                                                                                                                                                                                                     |

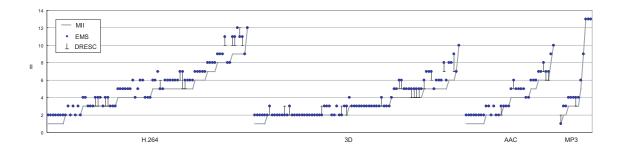

| 4.11 | Performance comparison of EMS and DRESC for the mesh-plus architecture                                                                                                                                                                                                                                                 |

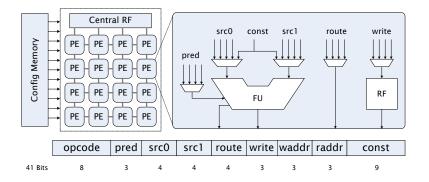

| 5.1  | CGRA overview: 4x4 array of PEs (left), a detailed view of a PE (right), and a PE instruction (bottom)                                                                                                                                                                                                                 |

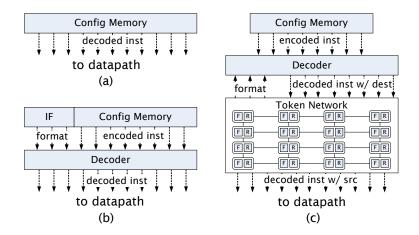

| 5.2  | Different Control Path Designs: (a) No compression, (b) Fine-grain code compression with static instruction format, (c) Fine-grain code compression with a token network (F and R indicate FU token module and RF token module, respectively)                                                                          |

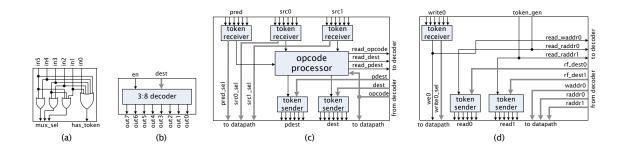

| 5.3  | Token Modules: (a) token receiver, (b) token sender, (c) FU token module, (d) RF token module                                                                                                                                                                                                                          |

| 5.4  | Dynamic configuration of PEs using tokens                                                                                                                                                                                                                                                                              |

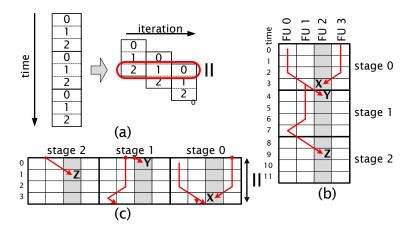

| 5.5  | Modulo scheduling basics: (a) Concept, (b) An example mapping for FU 2, (c) Kernel mapping                                                                                                                                                                                                                             |

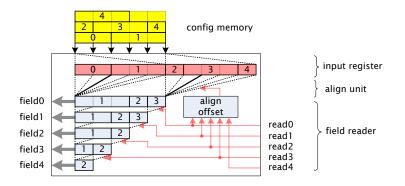

| 5.6  | Decoder for fine-grained code compression                                                                                                                                                                                                                                                                              |

| 5.7  | (a) Configuration memory partitioning, (b) Performance, power and area comparison of control path designs                                                                                                                                                                                                              |

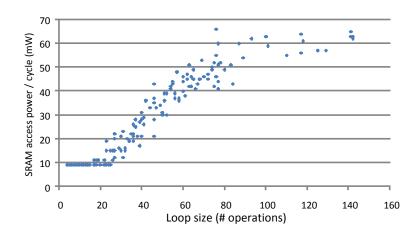

| 5.8  | Cache effect on SRAM power consumption                                                                                                                                                                                                                                                                                 |

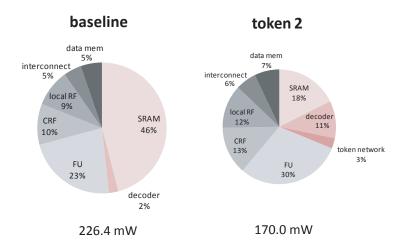

| 5.9  | Power breakdown of baseline and token 2 designs for a kernel loop in      |     |

|------|---------------------------------------------------------------------------|-----|

|      | H.264                                                                     | 103 |

| 6.1  | (a) CGRA loop accelerator, (b) Impact of the array size on the perfor-    |     |

|      | mance                                                                     | 106 |

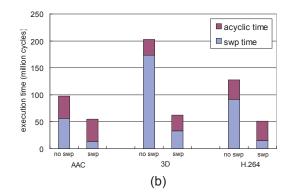

| 6.2  | (a) Number of software pipelineable loops, (b) Breakdown of execution     |     |

|      | time for software pipelineable region and acyclic region                  | 109 |

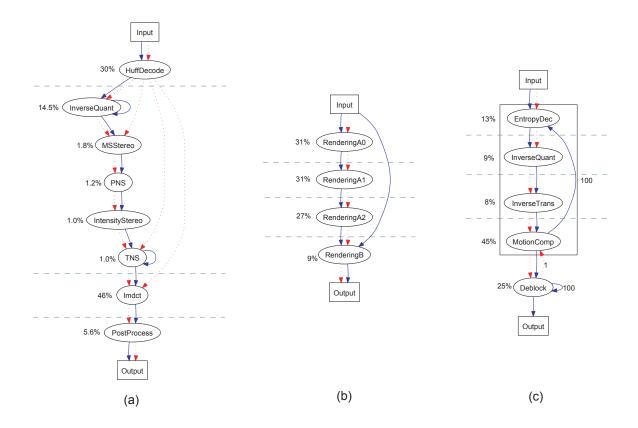

| 6.3  | Task Graphs: (a) AAC, (b) 3D, (c) H.264, nodes represent tasks, solid     |     |

|      | edges show control flow, and dotted edges show data transfer              | 110 |

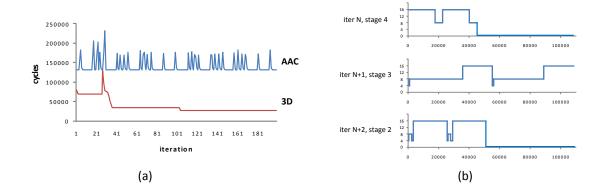

| 6.4  | Execution Pattern Variation in Coarse-Grain Pipelining: (a) Stage Ex-     |     |

|      | ecution Time, (b) Resource Requirements                                   | 113 |

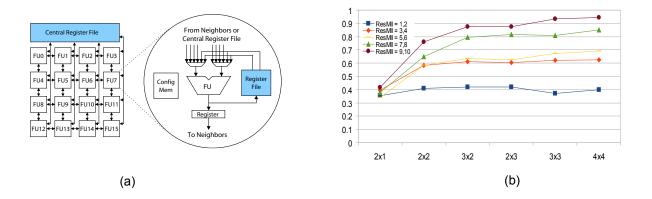

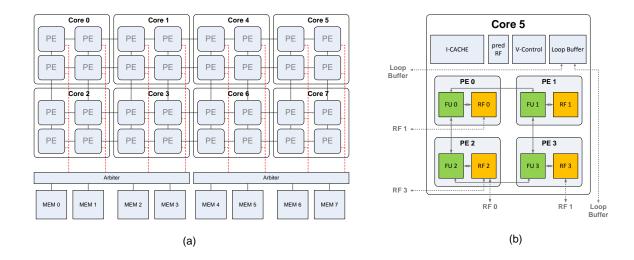

| 6.5  | PPA Overview: (a) PPA with 8 cores, (b) Inside a single PPA core .        | 117 |

| 6.6  | (a) An example of PPA running AAC in a pipelining fashion, (b) Vir-       |     |

|      | tualization Controller                                                    | 119 |

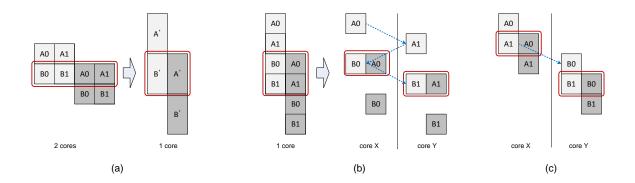

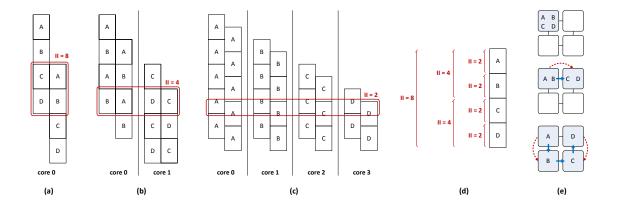

| 6.7  | (a) Folding with interleaving, (b) Expanding with horizontal cut, (c)     |     |

|      | Expanding with vertical cut                                               | 126 |

| 6.8  | (a) Execution in a single core, (b) Execution in two cores, (c) Execution |     |

|      | in four cores, (d) Multi-level modulo constraints, (e) Code expansion     | 128 |

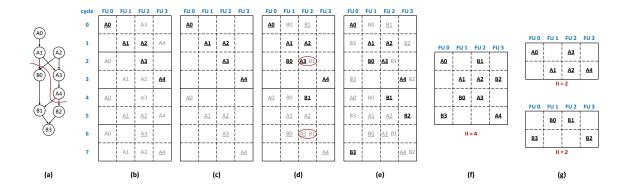

| 6.9  | (a) Dataflow graph, (b) - (e) Mapping examples, (f) Modulo schedule       |     |

|      | for 1x1 array, (g) Modulo schedules for 1x2 array                         | 130 |

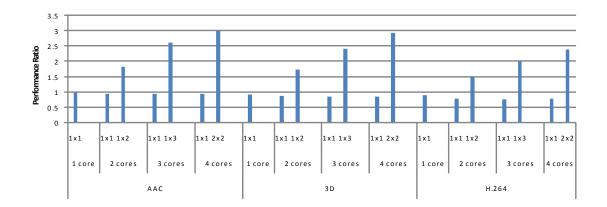

|      | Performance Evaluation of VMS                                             | 134 |

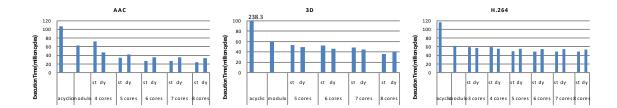

|      | Performance Evaluation of PPA                                             | 137 |

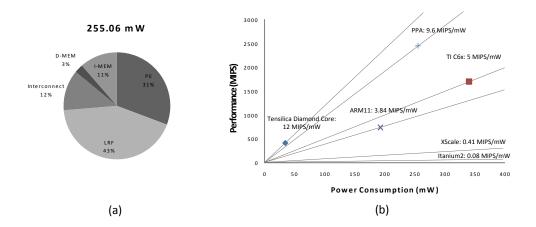

| 6.12 | (a) Power breakdown of PPA: running H.264, (b) Power/performance          |     |

|      | comparison                                                                | 140 |

# LIST OF TABLES

| Table      |                                                                          |    |

|------------|--------------------------------------------------------------------------|----|

| 3.1        | Register file configurations for three CGRA designs used for evaluation. | 34 |

| 3.2        | Effectiveness of the affinity heuristic using acyclic scheduling         | 36 |

| 3.3        | Modulo graph embedding results for the dedicated register file CGRA.     | 36 |

| <i>4</i> 1 | Compile time comparison (in seconds)                                     | 79 |

ABSTRACT

POLYMORPHIC PIPELINE ARRAY: A FLEXIBLE MULTICORE

ACCELERATOR FOR MOBILE MULTIMEDIA APPLICATIONS

by

Hyunchul Park

Chair: Scott A. Mahlke

Mobile computing in the form of smart phones, netbooks, and PDAs has become

an integral part of our everyday lives. Moving ahead to the next generation of mo-

bile devices, we believe that multimedia will become a more critical and product-

differentiating feature. High definition audio and video as well as 3D graphics pro-

vide richer interfaces and compelling capabilities. However, these algorithms also

bring different computational challenges than wireless signal processing. Multimedia

algorithms are more complex featuring more control flow and variable computational

requirements where execution time is not dominated by innermost vector loops. Fur-

ther, data access is more complex where media applications typically operate on

multi-dimensional vectors of data rather than single-dimensional vectors with sim-

хi

ple strides. Thus, the design of current mobile platforms requires re-examination to account for these new application domains.

In this dissertation, we focus on the design of a programmable, low-power accelerator for multimedia algorithms referred to as a *Polymorphic Pipeline Array* (PPA). The PPA design is inspired by coarse-grain reconfigurable architectures (CGRAs) that consist of an array of function units interconnected by a mesh style interconnect. The PPA improves upon CGRAs by attacking two major limitations: scalability and acceleration limited to innermost loops. The large number of resources are fully utilized by exploiting both fine-grain instruction-level and coarse-grain pipeline parallelism, and the acceleration is extended beyond innermost loops to encompass the whole region of applications.

Various compiler and architectural optimizations are presented for CGRAs that form the basic building blocks of PPA. Two compiler techniques are presented that systematically construct the schedule with intelligent heuristics. Modulo graph embedding leverages graph embedding technique for scheduling in CGRAs and edge-centric modulo scheduling provides a communication-oriented way to address the scheduling problem. For architectural improvement, a novel control path design is presented that leverages the token network of dataflow machines to reduce the instruction memory power.

The PPA is designed with flexibility and programmability as first-order requirements to enable the hardware to be dynamically customizable to the application. A PPA exploit pipeline parallelism found in streaming applications to create a coarse-

grain hardware pipeline to execute streaming media applications. PPA resources are allocated to each stage depending on its size and ability to exploit fine-grain parallelism. For dynamic partitioning of resources, Virtualized modulo scheduling generates a unified schedule that can be easily converted to target different number of resources at run-time.

## CHAPTER 1

#### Introduction

Mobile computing has become a ubiquitous part of society. More than half the world's population now owns on a cell phone, and in some countries, the number of active cell phone contracts out numbers the population. The embedded computer systems that power mobile devices demand high performance and energy efficiency to operate in an untethered environment. Traditionally, hardwired accelerators have done the heavy lifting in terms of computation. Mobile platforms are designed as heterogeneous systems-on-a-chip consisting of multiple processors (general-purpose and/or digital signal processors) and special purpose accelerators constructed for the most compute-intensive tasks. The performance/energy point achieved by these designs is impressive - performing tens of giga-operations per second at sub-Watt power levels.

Moving forward, there is a need to create more programmable mobile computing platforms. Programmable solutions offer several key advantages:

• Multi-mode operation is enabled by running multiple application standards

(e.g., two video codecs) or even multiple applications on the same hardware.

Accelerator-based solutions require a union of hardware blocks to accomplish all desired applications.

- Time to market of an implementation is lower because the hardware can be re-used across multiple platforms. More importantly, hardware integration and software development can progress in parallel.

- Prototyping and software bug fixes are enabled on existing silicon with a software change. On-going evolution of specifications are supported in a natural way by allowing software changes after the chipset and even the device have been manufactured.

- Chip volumes are higher as the same chip can support multiple standards without requiring hardware changes.

Traditionally, the design of programmable mobile computing platforms has focused on software defined radio [4, 3, 17, 35, 58]. These systems are geared towards wireless signal processing that contain vast amounts of vector parallelism. As a result, single-instruction multiple-data (SIMD) hardware is recognized as an effective strategy to achieve both high-performance and programmability. SIMD provides high efficiency because of its regular structure, ability to scale lanes, and low control cost. However, mobile computing systems are not limited to wireless signal processing. High-definition video, audio, 3-D graphics, and other forms of media processing are high value applications for mobile terminals. In fact, many believe the quality and

types of media support will be the key differentiating factors of future mobile terminals.

Media applications in a mobile environment offer a number of different challenges than wireless signal processing. First, the complexity of media processing algorithms is typically higher than signal processing. Computation is no longer dominated by simple vectorizable innermost loops. Instead, loop bodies are larger with significant amounts of control flow to handle the different operating modes and inherent complexity of media coding. This results in differential dynamic computational requirements. Further, significant time is spent in outer loops and acyclic code regions. As a result, SIMD parallelism is less prevalent and less efficient to exploit in media algorithms [37]. Second, the data access complexity in media processing is higher. Signal processing algorithms typically operate on single dimension vectors, whereas video algorithms operate on two or three dimensional blocks of data where the block size is variable. Thus, video and other forms of media processing push designs to have higher bandwidth and more flexible memory systems. Finally, the power budget is generally more constrained for media processing than wireless signal processing because of higher usage times.

To address these challenges, this work focuses on the design of a flexible media accelerator for mobile computing referred to as a *polymorphic pipeline array* or PPA. Our design does not exploit SIMD parallelism, but rather relies on two forms of pipeline parallelism: coarse-grain pipeline parallelism found in streaming applications [19, 20, 27] and fine-grain parallelism exploited through modulo scheduling

of innermost loops [48]. The PPA consists of an array of simple processing elements (PEs) that are tightly interconnected by a scalar operand network and a shared memory. Groups of four PEs form cores that are driven by a single instruction stream. These cores can execute tasks (filters in a streaming application) independently or neighboring cores can be coalesced to execute loops with high degrees of parallelism. The use of a regular interconnection fabric allows the core boundaries to be blurred, thereby allowing the hardware to be customized differently for each application.

The PPA design is inspired by coarse-grain reconfigurable architectures (CGRAs) that consist of an array of function units interconnected by a mesh style interconnect [38, 39]. In CGRAs, small register files are distributed throughout the array to hold temporary values and are accessible only by a small subset of function units. Example commercial CGRA systems that target mobile devices are ADRES [39], MorphoSys [36], and Silicon Hive [47]. Tiled architectures, such as Raw, are closely related to CGRAs though are not intended for mobile computing [52]. The abundance of resources in CGRAs offer large raw computation capabilities while the distributed nature of hardware and simple control provide low energy efficiency.

In this dissertation, we first attack the major challenges for deploying CGRAs in embedded environments. Two compilation techniques for efficient mapping of applications onto the highly distributed architectures like CGRAs are proposed. Also, a novel design of control path in CGRAs is proposed for reducing instruction read power. These optimizations can be directly applied to the PPA since it builds on the basic building blocks of CGRAs. Then, we provide the application analysis that

motivates the PPA design paradigm, the hardware description of PPA, and a new compilation technique to maximize the utilization of the proposed PPA.

## 1.1 Optimizations for CGRAs

#### 1.1.1 Compiler Support

The most difficult challenge in deploying CGRAs arises in the compiler support. An effective compiler is essential for exploiting the abundance of computing resources available on a CGRA. However, sparse connectivity and distributed register files present difficult challenges to the scheduling phase of a compiler. Traditional schedulers that just assign an FU and time slot to each operation are insufficient because they do not take routing into consideration. Scalar operand values must be explicitly routed between producing and consuming operations. Further, dedicated routing resources are not provided. Rather, an FU can serve either as a compute resource or as a routing resource at a given time. A compiler scheduler must thus manage the computation and flow of operands across the array to effectively map applications onto CGRAs. Chapter 2 provides the overview of CGRAs and major scheduling challenges.

This dissertation proposes novel scheduling techniques that collectively synthesize an efficient mapping of an application to the CGRA with a reasonable compile time. Specifically, the new techniques are developed in the context of modulo scheduling. Modulo scheduling is a software pipelining technique that overlaps the execution of loop iterations to provide the opportunity to exploit both loop-level and instruction-level parallelism. Modulo scheduling is especially effective for CGRAs since they provide a large number of resources for exploiting potential parallelism.

In Chapters 3 and 4, we propose two modulo scheduling approaches that differ in their primary objective of scheduling and we categorize them as node-centric and edge-centric approaches. The first approach in Chapter 3, referred as *modulo graph embedding*, is a modulo scheduling technique for CGRAs that leverages graph embedding commonly used in graph layout and visualization. This technique is node-centric in that the focus of scheduling is assigning operations (nodes in dataflow graphs) to FUs, just as in traditional schedulers.

The second approach in Chapter 4, on the other hand, considers routing operands between operations (edges in dataflow graphs) as its primary objective. Operation assignment to FUs can be viewed as a by-product of a successful route, thus no successive placement step is required. In essence, by getting an operand between two points, the necessary operations can be performed along the way for free. We refer to this technique as edge-centric modulo scheduling, or EMS.

## 1.1.2 Control Path Optimization

A major bottleneck for deploying CGRAs into a wider domain of embedded devices lies in the control path. The appealing features in the datapath of CGRAs ironically come back as a major overhead in the control path. The distributed interconnect and register files require a large number of configuration bits to route values across the network. The abundance of computation resources simply adds up the list for configurations to the control path. As a result, the total number of control bits to configure the whole array can reach nearly 1000 bits each cycle, and the control path takes up to 43% of the total power consumption in existing CGRA designs [25, 5]. In Chapter 5, we propose a novel control path design in CGRAs that leverages a token network in dataflow machines to improve the code efficiency.

## 1.2 Polymorphic Pipeline Array

The major weakness of CGRAs is their lack of ability to accelerate an entire application. Chapter 6 propose a flexible multicore accelerator that can accelerate multiple regions of a target application. The PPA shares the inherent hardware efficiency of CGRAs: fully distributed register files, nearest neighbor interconnect and simple control. An application study is performed to discover the available parallelism in today's mobile multimedia applications. The result of this study motivates the design of PPA that can support multiple levels of parallelism. Also, a novel scheduling technique is proposed that enables virtualized execution of loops.

## CHAPTER 2

## Background and Motivation

## 2.1 CGRA Overview

A CGRA consists of an array of compute nodes, each of which executes word-level operations, communicating through an interconnection network. In general, CGRA designs can be described by four characteristics: size, node functionality, network configuration, and register file sharing. The *size* refers to the number of nodes; commonly this can vary from 4 nodes arranged in a row up to 64 nodes arranged in an 8×8 grid. The *functionality* of each node can vary from a single FU (e.g. adder or subtracter), to an ALU, to a full-blown processor. In addition, the functionality of nodes may be homogeneous or heterogeneous. For example, only a subset of nodes may access data memory.

There are a large number of potential *network configurations*, such as connections between each node and its four (or eight diagonal) nearest neighbors, buses connecting each node to (possibly to a subset of) other nodes in the same row or column,

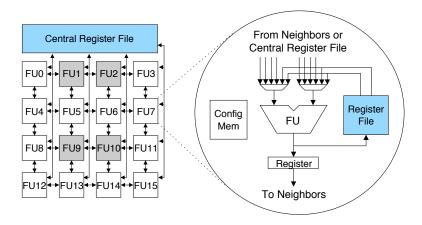

Figure 2.1: Example CGRA design

hierarchical connection schemes, and so on. Finally, the degree of register file sharing ranges from small, individual register files at each node, to multiple register files each shared by a small number of nodes, to a single central register file accessible by some or all nodes.

Figure 2.1 shows a CGRA design that contains 16 nodes arranged in a 4×4 mesh; each node can communicate with its four nearest neighbors. In addition, column buses connect each node to a central register file. Each node consists of an FU that can read inputs from neighbors or the central register file and write to a single output register; a small, dedicated register file; and a configuration memory to supply control signals to the MUXes, FU, and register file. Certain operations, such as loads and stores, can only be executed on a subset of FUs (shaded). Note that a node can either perform a computation or route data each cycle, but not both, as routing is accomplished by passing data through the FU. This architecture is only one possible CGRA design; many other variations are possible.

## 2.2 Modulo Scheduling Challenges

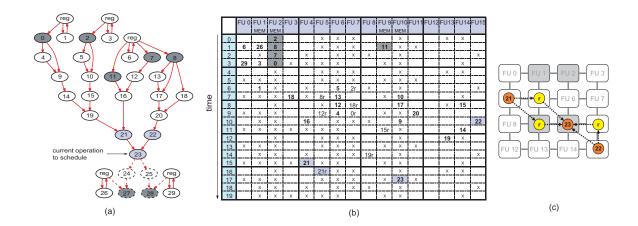

Figure 2.2: Example to illustrate the challenges of CGRA scheduling: (a) the dataflow graph for the fsed application, (b) the reservation table for a partial schedule on a 4x4 array, (c) possible routings from 23's producers. In (a) and (b), dark grey shading indicates memory operations and light grey shading is used to highlight the current operation being scheduled (node 23) and its immediate predecessors. Bold numbers indicate computation operations, other numbers followed by 'r' (e.g. '8r') indicate routing slots for corresponding computation operations. 'reg' nodes indicate live-in values stored in the central RF.

Modulo scheduling is a software pipelining technique that exposes parallelism by overlapping successive iterations of a loop [48]. The goal is to find a valid schedule such that the interval between successive iterations (initiation interval, or II) is minimized. The II-cycle code region that achieves this maximal overlap is called the kernel. When the number of iterations is large, the performance of the loop is determined by the II to a first order; thus, it is more important to minimize the II than to minimize schedule length. Initially, the scheduler chooses the target II to be the maximum of the resource-constrained lower bound (ResMII) and the recurrence-constrained lower bound (RecMII). If a valid modulo schedule cannot be found, the target II is

incremented and scheduling is attempted again.

Scheduling for CGRAs is quite different from scheduling for general VLIW architectures due to the different hardware characteristics. Factors that complicate CGRA scheduling include:

**Explicit routing.** In a VLIW architecture, routing from producer to consumer is implicitly guaranteed by storing intermediate values in a multi-ported, centralized register file. However, in a CGRA, interconnect is much more sparse and values must be explicitly routed using FUs, local register files, and mesh connections.

Intelligent routing. FUs are used for both computation and routing; thus, scheduling can easily fail if poor routing choices are made. Furthermore, the scheduler must not only generate a valid schedule, but also minimize the routing resources used so that more FUs are available for computation.

Heterogeneous nodes. All nodes can perform addition and logical operations, but "expensive" operations such as multiplies, loads, and stores may only be supported by a subset of nodes. In such an architecture, it is important to avoid scheduling inexpensive operations on expensive nodes, because this limits the scheduling flexibility of the expensive operations.

Modulo constraint. Resources are used in a periodic fashion, since the loop kernel repeats every II cycles. Thus, unlike in acyclic scheduling, it is not possible to guarantee routability by extending the schedule, and scheduling can easily fail due to the previously scheduled operations.

To illustrate the complexities of CGRA modulo scheduling, Figure 2.2(a) shows

the dataflow graph (DFG) for the dominant loop from one of our benchmark applications, fsed, an image halftoning algorithm. Memory operations are shaded dark grey. The DFG is being scheduled onto a 4×4 CGRA, similar to the one shown in Figure 2.1, with II=4. The partial schedule is shown in Figure 2.2(b). schedule is shown. Bold numbers are computation operations; other numbers followed by 'r' (e.g. '8r') are routing operations for the corresponding computation operations; and, Xs represent slots that are occupied due to the modulo constraint. 'reg' nodes indicate live-in values that are stored in the central RF. All operations above operation 23 (light grey) in the DFG have been scheduled at this point.

There are several points to observe. First, only FUs 1, 2, 9, and 10 support memory operations, thus all of the memory operations must be scheduled on those FUs. Next, observe how values are routed to operation 23, which is considered for execution on FU 10 at time 17, and has two producers: 21 and 22. Figure 2.2(c) shows the possible routes of the operands from two producers. One possible way to route the operand from 21 to 23 is through FU 9. The operand is first routed diagonally from FU 4 to FU 9 via a shared register fie, then it is routed to the neighboring FU 10 via the mesh connection. However, taking this option leaves only two memory slots for the unscheduled memory operations (27 and 28). Therefore, the operand of 21 is routed through FU 5 rather than through FU 9. Similarly, the operand of 22 is routed directly from FU 15 to FU 10 rather than through FU 11. The value is stored in a rotating register file for 6 cycles and is read out by 23 at time 17. The challenge here is how to guarantee the availability of storage in the register file. The available

storage must be carefully considered during scheduling as simply pushing register allocation to after scheduling can result in costly spilling and may require complete rescheduling of the loop. It can be seen that routing is complex, and various resources including FUs, registers, register file ports, and connection links must be modeled by the compiler to properly orchestrate the flow of values from producers to consumers. Further, this routing adds latency to the schedule: operation 23 has an earliest start time of 11, but is actually scheduled at time 17.

## CHAPTER 3

## Modulo Graph Embedding

#### 3.1 Introduction

In this chapter, we propose a modulo scheduling technique for CGRA architectures that leverages graph embedding commonly used in graph layout and visualization [33], referred to as modulo graph embedding. Graph embedding is a technique in graph theory in which a guest graph is mapped onto a host graph. With CGRAs, scheduling is reduced to placing operations of a loop body on a three dimensional grid. The three dimensions consist of the FU array that comprises two dimensions and the time slots of a modulo scheduled loop that form the third dimension.

Modulo scheduling is performed by considering groups of equal height operations from the top of the dataflow graph (DFG) to the bottom. The three dimensional scheduling grid is filled in a skewed manner by restricting the subset of FUs and time slots available for each group of operations. This stylization increases routability of operands and can dynamically adapt to different shape DFGs. A discrete cost

function between pairs of DFG nodes is designed and the placement algorithm tries to reduce this cost function. The cost function consists of different components: routing cost, which ensures that producers and consumers are placed close to one another; affinity cost, which ensures that operations with common consumers are placed close together; and, position cost, which ensures that operations are left-justified on the set of eligible resources. Left justification ensures operations are tightly packed and enables operand routing to subsequent operations using the righthand portion of the array.

The central advantages of modulo graph embedding are summarized as follows:

- It scales well with respect to number of operations in the DFG and thus is capable of handling large loop bodies.

- It handles a wide variety of CGRA configurations, including sparse interconnect and fully distributed register files.

- It is a systematic technique that assigns operations to the nodes in a CGRA and thus convergence to a solution is faster along with producing higher quality schedules.

## 3.2 Modulo Graph Embedding

This section describes modulo graph embedding, our approach to modulo scheduling for CGRAs. We break the description down into two parts: Section 3.2.1 presents the important concepts of the approach in isolation, and Section 3.2.2 brings every-

thing together to discuss the complete scheduling algorithm.

#### 3.2.1 General Concepts

#### 3.2.1.1 Resource and Connectivity Management

During instruction scheduling, a reservation table is maintained to keep track of which resources are used in each time slot. As resources are repeatedly used every II cycles by successive iterations of the loop, the modulo scheduler maintains a Modulo Reservation Table (MRT) which has only II time slots [48]. Considering that the scheduler for a CGRA must perform routing of values as well as placement of operations, routing information should be recorded by the scheduler. This routing information can be included in the reservation table because FUs are used both for computation and routing. Management of the interconnect network is not necessary as all of the connections are dedicated point-to-point connections, meaning that no congestion can occur in the network.

For resource management, the concept of the Modulo Routing Resource Graph (MRRG) from the DRESC compiler framework [38] is used. The MRRG is a graphical representation of the scheduling space where nodes represent routing resources and edges describe the connectivity of those resources. Scheduling in the CGRA becomes a problem of placement and routing of each operation on the MRRG.

The original MRRG has a detailed description of the CGRA [38]. MRRG nodes are created for each port on the FUs and register files, in addition to the MRRG nodes for the FUs and register files themselves. We take a simplified approach to

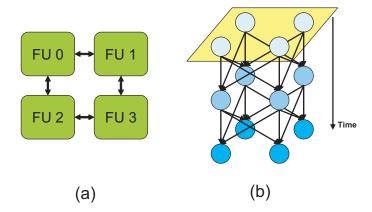

**Figure 3.1:** Modeling resources in a CGRA: (a) example 2x2 CGRA, (b) resource management model for 2x2 CGRA with II=3.

model the CGRA. A single node is created for each FU and register file. Since port information for FUs can be easily discovered by analyzing the resulting schedule along with the instruction format, it is not necessary to create nodes for the individual FU ports. Port information for register files can also be discovered in the same way, but two additional nodes are used to limit the number of read/write accesses to register files. Our resource management model can be considered as a distributed MRT with connectivity information. Each node represents either an FU or register file and is equipped with a MRT to keep track of the resource usage.

Figure 3.1(b) shows our resource management model constructed for the 2x2 CGRA in Figure 3.1(a) with II = 3. Nodes for register files and wrap-around edges were omitted for simplicity. Each of the four nodes in the CGRA has a 3-entry MRT, and each edge specifies that a value can be routed from the source to the destination resource. When an operation is placed on an FU, the MRT in the corresponding node is marked as occupied at the schedule time. If there are any placed producers or consumers, a valid route is discovered by traversing nodes along the edges.

#### 3.2.1.2 Register Assignment and Allocation

With modulo scheduling, the number of registers required by a loop is not known before scheduling. In addition to conventional register allocation constraints, it may be necessary to keep multiple copies of registers depending on how many iterations separate the first producer and last consumer. This can cause a problem for the small, distributed register files in CGRAs as the number of total registers required at a single FU can exceed the local register file capacity. The available storage must be carefully considered during scheduling as simply pushing register allocation to after scheduling can result in costly spilling and may require complete rescheduling of the loop.

Our approach is to perform a simple register allocation and assignment during modulo scheduling. The modulo constraint that is enforced for FUs is also enforced for registers, i.e., there is an MRT kept for the each register file. A register value can stay in the same register up to II cycles, but the value will be overwritten by the same instruction in the next iteration II cycles later. When a register value is live for longer than II cycles, it has to be explicitly routed to another register file (or to another register in the same file). Specific entries in the register file are allocated for each virtual register using a simple greedy algorithm. While this approach may seem overly simplistic, it effectively guides the scheduler to distribute register usage across the CGRA.

**Figure 3.2:** Example showing the placement of producers affects the routing cost of consumers: (a) DFG for loop, (b) target architecture which is a 1x4 CGRA, (c) poor schedule that results in an extra cycle for routing values to Op 6, and (d) good schedule that results in no additional routing.

#### 3.2.1.3 Height-based Scheduling

The problem of modulo scheduling for a CGRA can be viewed as mapping applications onto the 3-D space consisting of the FU array stacked up II times. With this finite scheduling space, minimizing the routing cost is a critical issue in scheduling, as fewer resources being used for routing leads to more resources being available for computation. Routing cost is defined as the number of FUs being used for routing (passing data from one node to another) rather than computation. This cost depends on the positions of producer and consumer operations in the CGRA due to the sparse interconnect network. This requires the scheduler to be cognizant of producer and consumer relations so that they can be placed close to each other.

Figure 3.2 shows how the placement of operations impacts the routing cost of their consumers. Figure 3.2(a) is an example DFG and Figure 3.2(b) is a hypothetical architecture with sparse interconnect where FUs are allowed to communicate only

with adjacent FUs. Figures 3.2(c) and Figure 3.2(d) show two different schedules, both minimizing the routing cost for operations 4 and 5. When operation 6 is placed, the minimal routing cost is affected by the positions of its two producers (operations 4 and 5). This suggests that the scheduler must proactively choose placements to reduce routing costs.

To effectively manage routing costs, we employ two complementary techniques: height-based scheduling and the affinity-based placement which is discussed in the next section. Height-based scheduling is a common heuristic used in list scheduling where operations are scheduled in the order of dependence height. Operations with greater height are scheduled first, followed by operations with lower height. But, for operations with the same height, a CGRA scheduler cannot process them individually because placement of one operation has cost implications on the placement of others. Careless placement of one operation might increase the routing cost of other operations, or even make it impossible to place by blocking all of its routing possibilities. Therefore, operations with the same height are considered together to achieve an optimal placement rather than being scheduled separately. Possible schedule slots (resource/time pairs) are identified for each operation, and a combination of schedule slots (called a layout) that minimizes the total routing cost is selected.

#### 3.2.1.4 Affinity Graph

Routing cost is difficult to minimize during scheduling because the true cost is not known until all producer-consumer pairs are placed. With height-based scheduling, consumers are generally placed after the producers (except for operations on a recurrence cycle). Therefore, routing cost associated with just the producers is considered when an operation is placed. Even though the routing cost associated with consumers cannot be measured at the time that the producers are scheduled, it is desirable to account for these consumers in some way to avoid making greedy decisions. Ideally, operations with a common consumer should be placed close to each other so that the routing cost can be minimized later.

A measure of affinity is utilized to perform more intelligent scheduling by using information about common consumers. The affinity between a pair of operations with the same height is a measure of how close their common consumer is in the DFG. Operations with an immediate common consumer have the highest affinity between them, while operations without a common consumer have zero affinity. Operations with indirect common consumers have moderate affinities that decrease based on the distance to the common consumer. The goal is to place operations with high affinity close together to minimize the routing cost of the common consumers.

For each pair of operations, the affinity is calculated by looking at their common consumers. An affinity graph is then constructed that consists of nodes representing operations and edges representing affinity between operations. An example of the affinity graph is shown in Figure 3.3. The affinity graph is constructed for the operations in the first row of the DFG in Figure 3.3(a). Figure 3.3(c) is the resulting affinity graph where solid edges represent high affinity between operations (a value of 2 in the example) and dotted edges represent low affinity between operations (a

**Figure 3.3:** Example affinity graph: (a) DFG for loop, (b) calculated affinities between each pair of operations, (c) affinity graph, and (d) possible operation assignments to a 2x4 CGRA.

value of 1). Pairs of operations without edges have an affinity of zero.

For each pair of operations A and B with the same height, the affinity value is calculated using the following equation. Only the common consumers within the range of  $max\_dist$  are considered in the calculation of the affinity value. The variable  $num\_cons(A,B,d)$  denotes number of common consumers of A and B whose distance from A and B in the dataflow graph equals d.

$$affinity(A,B) = \sum_{d=1}^{max\_dist} 2^{max\_dist-d} \times num\_cons(A,B,d)$$

(3.1)

When scheduling operations, the scheduler attempts to place operations close together according to their affinity. Two alternate schedules for the operations are shown in Figure 3.3(d) that illustrate the use of affinity to eliminate explicit routing operations by performing more intelligent assignment of operations to nodes in the CGRA. The schedule on the left is better because operations with affinity edges are

**Figure 3.4:** CGRA scheduling spaces: (a) normal scheduling space, (b) skewed scheduling space, (c,d,e) variations of skewed scheduling space.

placed closer on the array.

### 3.2.1.5 Graph Embedding

In this work, we leverage graph embedding that is commonly used in graph layout and visualization. Graph embedding is a particular drawing of a graph onto a target space (usually a planar space). Drawing large graphs "nicely" is not an easy task. Here, a nice graph usually refers to non-crossing edges and a regular distribution of nodes. The spring embedder model [10] is a well known heuristic approach to graph embedding. It simulates a mechanical model of rings attached with springs. Each ring represents a node in the graph and each spring between two rings represents forces that attract or repel the nodes in the graph. The spring embedder is a suitable model for our scheduling. Each weighted edge in the affinity graph can be thought of as a spring that attracts two nodes in the graph. An edge with high affinity will attract two operations so that they are placed on the same or nearby resources.

A large amount of research has been conducted for effective graph drawing using

the spring model. Kamada and Kawai proposed an iterative algorithm that calculates attractive and repulsive forces for each node and gradually moves the nodes with respect to the calculated forces [23]. Davidson and Harel employed a simulated annealing method that improves the cost of the graph based on the spring model [8]. However, most works do not fit into our scheduling problem as they assume a continuous space rather than the discrete, finite 3-D scheduling space. Graph embedding onto a grid-based space is well studied in the area of VLSI cell layout, known as force-directed placement. These works have somewhat different objectives, such as minimum edge bends. Li and Kurata proposed a grid layout algorithm of biochemical networks [33]. It uses simulated annealing for embedding complicated biochemical graphs onto the grid space. We found this solution best suited for our problem as its target space is discrete and the objective is placing nodes with edges close together.

Compared to the target graphs of typical graph embedding algorithms, our affinity graph has quite a small number of nodes. This is because we are not scheduling the whole application at one time. Instead, graph embedding is performed for each height level of the DFG and it is unusual for more than 20 operations to have the same height. Also, the search space is limited by pre-placed operations because pre-placed producers limit the possible slots of their consumers due to the sparse interconnect. For the search space that is sufficiently constrained, a simple exhaustive search can find an optimal layout of operations quickly. Li and Kurata's algorithm is employed only for large search spaces where the exhaustive search cannot finish in a reasonable time.

### 3.2.1.6 Skewed Scheduling Space

One of the difficult challenges of scheduling for CGRAs is ensuring that the necessary routing can take place as the CGRA is filled up with more operations. At the start of scheduling, the CGRA is empty, thus routing is not difficult. But, as scheduling proceeds, the scheduler can easily back itself into a corner and get stuck where the necessary routing cannot be performed. The affinity heuristic tries to minimize the overall number of resources used for routing, but this is not enough. When schedule times get larger than II, difficulties often result due to pre-placed operations (repeated resource use by the same operation every II cycles) and already-placed producers.

The conventional approach used in modulo scheduling is backtracking, where one or more operations are unscheduled to allow the current operation to successfully schedule [48]. However, backtracking for CGRAs is much more complicated. First, placing an operation usually requires more than one resource as routing is involved. This means that many operations can be unscheduled to overcome a routing failure. Moreover, re-scheduling operations requires both routing to its consumers as well as from its producers. It's difficult for the scheduler to make forward progress with backtracking.

A different approach is to prevent routing failures in advance. In general, routing failures to a consumer can be avoided if all the resources are free in time slots later than a producer's time slot. This is why the acyclic scheduling does not suffer from routing failures as it has an infinite scheduling space. Likewise, modulo scheduling does not suffer from routing failures within an II cycle window. Further, most applications

don't have enough parallelism that requires all the CGRA FUs in one cycle. These two observations encourage clustering of the CGRA. With clustering, the FUs in the CGRA are partitioned into subsets. The scheduler can utilize one subset, or cluster, without any routing failures for II cycles. When the cluster is full, the scheduler can then use another cluster for the remaining operations, and so on.

Instead of partitioning the CGRA statically, our approach clusters the CGRA dynamically where the cluster boundaries are not strictly defined. The clusters are formed in a left-to-right manner on the array. The scheduler gives priority to the leftmost available FUs. But when the application parallelism is high, the cluster is dynamically enlarged by being forced to assign operations to lower priority FUs on the right. The scheduler utilizes a position cost to accomplish dynamic partitioning. When an operation is considered on an FU, its position cost is computed. The position cost is determined by the column in which the FU lies. Low cost is assigned to the leftmost available FUs, while higher cost is assigned to the FUs that lie further to the right.

When a partition of FUs to the left becomes full, values must be routed to FUs to the right. To guarantee this is possible, the concept of a skewed scheduling space is introduced as shown in Figure 3.4(b). Unlike the traditional scheduling space (see Figure 3.4(a)) where all the slots are available at the given schedule time, the start times of FUs are restricted such that they stagger down the right side of the CGRA. Since each FU is only available later than the FU on its left, the last schedule slot is always available to the output value of the last schedule slot of its left FU.

When no operation is placed on an FU at the original start time, the start time increases, which slides down the scheduling space of the FU. When the scheduling space of an FU is lowered, scheduling spaces of FUs to its right are also lowered to guarantee the routability. Therefore, the skewed scheduling space dynamically changes as operations are placed in the CGRA. As the operations at the same height are considered together to get an optimal layout, the parallelism in the application at the given height determines the shape of the scheduling space. Some applications may not even require all four FUs in one column. In this case, the position cost is augmented with the row cost and the FUs in the upper rows are utilized first. Figure 3.4(c), (d) and (e) show several other possible skewed scheduling spaces.

Assignment of operations to the skewed scheduling space works well for forward dependence patterns, but difficulties arise with recurrence cycles. Recurrence cycles contain a communication pattern where a producer is scheduled after its consumer. Thus, the producer will be likely to be placed on the right of its consumer and routing becomes difficult since most schedule slots on the left are already utilized. To address this routing problem, our approach is to reserve in advance slots for such cycles when the consumer is placed. When a producer is placed later, it can use this reserved route. Again, we take the preventative approach to avoiding routing problems rather than solving them when they occur.

Figure 3.5: Overview of the CGRA scheduling system: input is the assembly code for the loop body and a description of the CGRA; preprocessing analyzes the loop to compute heights and skew the available scheduling cycles for the FUs; the graph is iteratively scheduled at successive dependence height levels by constructing the affinity graph and performing modulo graph embedding of the affinity graph on the CGRA.

## 3.2.2 Implementation

Figure 3.5 presents an overview of our system. It takes the target loop body and description of the CGRA as input. The scheduling process consists of an initial preprocessing step to analyze the DFG and set up the skewed scheduling space. This is followed by the main scheduling loop that iterates over each level of the DFG to find a placement of all the operations at a particular height using modulo graph embedding.

#### 3.2.2.1 Preprocessing

The target application is first preprocessed to calculate the heights of all operations based on the distance from the terminating operation (e.g., the loop back branch). The height of an operation determines when it is considered for scheduling and the height difference between producer and consumer is a rough estimation of the live range of the intermediate values.

The scheduling space is skewed by assigning different start times to FUs. The same start time is assigned to all FUs in one column. Starting from zero for the first column on the left, the start time staggers downward with each increasing column number.

### 3.2.2.2 Scheduling Process

Scheduling proceeds through successive dependence height levels of the DFG considering all operations at a level simultaneously. Scheduling is converted into a graph embedding problem that maps the affinity graph onto the skewed scheduling space. Our modulo scheduler is implemented based on Li & Kurata's grid layout algorithm [33]. In the remainder of this section, we review basic ideas behind grid layout and describe our modified algorithm.

Grid Layout: Grid layout treats graph embedding as an optimization problem. A discrete cost function is defined for each pair of nodes based on the topological relation and the geometric positions of the nodes in the layout. Namely, high cost is given when two nodes connected by an edge are placed far apart and low cost is given when they are placed close together. The cost of a layout is given as a summation of costs for all node pairs. Simulated annealing is employed to find the layout with the lowest cost.

Modulo Graph Embedding: Unlike the original problem in grid layout, our problem has more constraints and costs to consider. Specifically, scheduling operations at each height has the following objectives:

- Place operations with a common consumer close to each other

- Minimize the routing cost for values from producers

- Ensure the routability of values to consumers

To achieve the objectives above, the scheduling concepts in Section 3.2.1 are realized in a cost function composed of three terms: routing cost, affinity cost, and position cost. They are calculated for operations by the following equations. where A and B are operations to be placed and affinity(A, B) is given by Equation 3.1 from Section 3.2.1.4:

$$routing\_cost(A) = \# FUs \ used \ for \ routing \ values \ from \ producers \ to \ A$$

(3.2)

$$affinity\_cost(A, B) = distance(FU(A), FU(B)) \times affinity(A, B)$$

(3.3)

$$position\_cost(A) = column \# of FU(A) \times BASE\_COST$$

(3.4)

$$layout\_cost = \sum_{A \in ops} \Big( routing\_cost(A) + position\_cost(A) \Big) + \sum_{A,B \in ops} affinity\_cost(A,B)$$

$$(3.5)$$

Grid layout employs a simulated annealing search to find an optimal layout of operations at each level by minimizing *layout\_cost*. While the original grid layout maps a graph onto a 2-D plane, our target space is 3-D scheduling space which

can have an infinite search space with varying schedule times. Therefore, we limit the search space by placing operations only in slots that minimize routing cost, called primary slots. Primary slots are identified before placing any operations. Even though each individual primary slot has the same routing cost, the total routing cost of a layout might vary because routing for one operation might block routing for another. Therefore, the routing cost is still considered in the cost function.

Once primary slots are identified, the size of search space is the product of the size of each operation's primary slots. Sometimes the search space can be quite small since pre-placed producers limit the placement of consumers. For small search spaces, exhaustive search is employed rather than using the grid layout. A flow chart of the scheduling process is presented in Figure 3.6.

The grid layout process begins with an initial layout obtained by randomly placing operations in one of their primary slots. Beginning with the initial layout, the scheduler enters a loop where the cost of current layout is iteratively reduced using simulated annealing. First, operations are randomly moved or swapped with other operations to generate a neighbor of the current layout. The neighbor layout is then locally optimized. Local optimization greedily performs moving or swapping operations whenever the cost is reduced, and these actions are repeated until no further improvement can be achieved. The locally minimized layout is evaluated for acceptance as an optimal layout. At some points, an uphill movement is taken to escape from a local minimum. After the optimal layout is discovered, the scheduling space is adjusted to reflect the chosen placement of operations at the current height and the

**Figure 3.6:** Scheduling process for operations at each successive dependence height. scheduler proceeds to the next height.

### 3.2.2.3 Scheduling Example

The process of scheduling each height of the application onto the skewed scheduling space is illustrated in Figure 3.7 with sobel, an image edge detection algorithm. The II in this example is 4. Due to space limitations, scheduling of operations for the first three heights is presented. Figure 3.7(a) shows the DFG of sobel and the target 4x4 CGRA. Scheduling for the selected heights is illustrated in Figure 3.7(b).

For each height, the affinity graph for the operations is shown at the top with solid edges representing high affinity and dotted edges representing low affinity. The table in the middle, where FUs are represented horizontally and time vertically, shows the resulting layout of operations. Note that the FUs in the left two columns only appear in the table since the other FUs are not used in this example. Each entry in the table represents a schedule slot and shaded entries constitute the scheduling space of the CGRA (also shown in 3-D graph at the bottom). Since FUs are repeatedly used every II cycles, entries are marked with X's when they are occupied by previously

**Figure 3.7:** Example of modulo graph embedding: (a) DFG of sobel and target CGRA, (b) scheduling results of first three heights.

scheduled operations.

At height 11, operations are placed only in the first column due to the limit of the skewed scheduling space. Also, operations with high affinity represented in solid edges are placed in adjacent schedule slots. For example, 145 is placed adjacent to 165 and 143 due to its high affinity with these operations. Conversely, 145 is placed apart from 157 because there is no affinity between 145 and 157. Note that routing cost is not considered at this height since there are no producers placed.

At height 10, all the costs, including routing cost, are considered. As the operations at height 11 were intelligently placed based on the affinity, the scheduler places operations at height 10 without using any resources for routing. FUs in the second column are also utilized to support the parallelism in the application. Since no operation is placed on FU 7 at its original start time of 1, FU 7's start time is increased by 1 and its scheduling space is slid down. This also implies that the scheduling spaces

| Design Name  | #RFs      | #FUs   | #Regs | #Read | #Write |  |

|--------------|-----------|--------|-------|-------|--------|--|

|              |           | per RF |       | ports | ports  |  |

| Dedicated RF | 16        | 1      | 4     | 2     | 1      |  |

| Shared RF    | 4         | 4      | 12    | 8     | 4      |  |

| Central      | 16 local  | 1      | 4     | 2     | 1      |  |

| RF           | 1 central | 16     | 32    | 8     | 4      |  |

Table 3.1: Register file configurations for three CGRA designs used for evaluation.

of FU 11 and FU 15 are slid down to guarantee routability.

Operations at height 9 are scheduled similarly to those at height 10, again accounting for all costs. Note that the unoccupied slots in the second column at time 0 can be utilized II cycles later when output values of operations placed in the first column cannot otherwise be routed due to the modulo constraint. For example, the output values of operations 68 and 71 at height 9 can be routed using schedule slots of the second column at time 4.

The final scheduling space of sobel is shown on the righthand side of Figure 3.5.

## 3.3 Experimental Results

## 3.3.1 Experimental Setup

CGRAs can be characterized by many parameters. To evaluate the performance of our scheduler, three designs were tested. All three designs have the same architectural parameters except for their register file configuration. All are 4x4 homogeneous CGRAs connected with a mesh network, with operation latencies of the ARM926 (e.g., 3 cycles for multiply, 2 cycles for load/store, and 1 cycle for simple arithmetic).

Table 3.1 shows the register file configurations for the three designs. These designs are the same as those pictured in Figure 2.1. The central RF design is the same as the dedicated RF design except that it has an additional central register file shared by all 16 FUs.

To evaluate the modulo graph embedding scheduler, twelve loop kernels are taken from various application domains: signal processing (fft, fir, iir, viterbi), encryption (blowfish), image processing (dct, fsed, sharp, sobel), network processing (channel), and video compression (idct, dequant). Only the innermost loop is considered for modulo scheduling for multidimensional loop nests.

## 3.3.2 Evaluation of Affinity Graph Heuristic

The main objective of the affinity graph heuristic is to minimize total routing cost by using common consumer information. In modulo scheduling, total routing cost is affected by other factors, such as recurrence cycles and the modulo constraint. In acyclic scheduling, we can exclude the influence of the modulo constraint as we can always find time slots where resources are available by increasing schedule time. Thus, we evaluated the performance of our affinity graph heuristic in the domain of acyclic scheduling; only loop kernels without a constraining recurrence cycle were tested. The dedicated RF design in Figure 2.1(a) was used as the target architecture because it has the sparsest interconnect and therefore is the most affected by the placement heuristic.

Two cost models were compared to evaluate the affinity graph heuristic. One is